中芯國際無 EUV 製程下的 5nm 技術突破 - 製程華為Kirin 晶片準備量產但仍差 TSMC 的很遠

中芯國際(Semiconductor Manufacturing International Corporation,SMIC)作為中國最大晶圓代工廠,據報導正在不使用極紫外光刻(EUV)設備的情況下,推進其製造能力以為華為生產 5nm 晶片,這一技術里程碑可能重塑全球半導體格局。這一發展代表著中國在美國出口限制下追求半導體自主的重大成就。

中芯國際先進製造現況

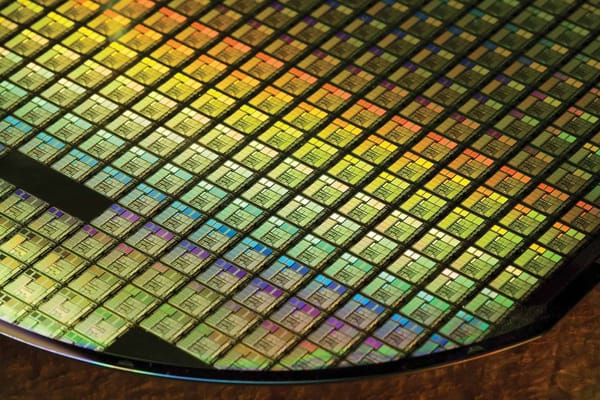

中芯國際在先進晶片製造方面已經展現出相當的進展,特別是其 7nm 製程。TechInsights 確認中芯國際的 7nm N+2 製程被用於製造華為 Mate 60 Pro 智能手機中的麒麟 9000s SoC。N+2 製程相較於之前的 N+1 有所改進,從分析師所描述的「勉強達到 7nm 製程」進步到「完全符合 7nm 製程標準」。

使用該製程製造的麒麟 9000s 晶片尺寸為 107 平方毫米,比之前的麒麟 9000(105 平方毫米)大約大 2%。這一成就標誌著中國晶圓廠首次在無 EUV 設備的情況下商用最先進的邏輯製程節點,支持完整的系統級晶片功能元素。

對 N+2 製程的分析顯示,雖然其接觸多晶間距(CPP)和金屬 2 間距(M2P)比 N+1 製程更緊湊,但它們仍不如台積電的 7nm 產品緊湊。然而,N+2 的整體高密度邏輯晶體管密度介於台積電的 7nm 和 7nm+ 之間,使其成為具有競爭力的 7nm 製程。

無 EUV 實現 5nm 的技術方法

DUV 與多重曝光技術

中芯國際實現 5nm 製造而不使用 EUV 的方法依賴於較舊的深紫外(DUV)光刻設備,結合複雜的多重曝光技術。具體而言,公司正在實施自對準四重圖案化(SAQP),這是一種複雜的工藝,允許實現通常需要 EUV 系統才能達到的超精細圖案。

傳統光刻在先進節點上面臨解析度限制。雖然 EUV 技術通過其較短波長克服了這些限制,但中芯國際必須採用多次曝光和蝕刻步驟,才能使用 DUV 設備達到類似的結果。這一過程包括:

- 光刻-蝕刻-光刻-蝕刻-光刻-蝕刻(LELELE)間距分割用於三重圖案化

- 對 5nm 特徵需要更複雜的四重圖案化

- 浸潤式光刻使用水作為介質以提高解析度

據報導,華為和中芯國際已經提交了使用 SAQP 的晶片生產方法專利,該方法涉及在矽晶圓上多次蝕刻線條以增加晶體管密度。華為專利申請中描述的 SAQP 方法旨在提高晶體管密度,降低功耗,並可能提升性能。

發展時間表與預測

根據多份行業報告,中芯國際有望在 2025 年完成 5nm 製程開發。一些消息來源甚至表示,中芯國際可能會在今年(2025 年)為華為製造 5nm 晶片。

韓國金融服務公司 Kiwoom Securities 預測,中芯國際將在 2025 年的某個時間點完成 5nm 製程的開發,這些晶片可能為華為的 Ascend 910C AI 加速器提供動力。

成本和效率挑戰

生產成本

在沒有 EUV 的情況下製造 5nm 晶片的成本帶來了重大挑戰。報告指出,中芯國際的 5nm 晶圓可能比台積電使用 EUV 技術生產的晶圓成本高 40-50%。這一顯著的價格溢價反映了使用 DUV 設備進行如此先進節點時所需的額外處理步驟和複雜性。

前台積電研發副總裁林本堅(Burn Lin)是浸潤式光刻技術的創新者,他表示,使用 DUV 設備製造 5nm 晶片至少需要四重圖案化——這一過程本質上耗時且昂貴。能夠以每小時 250 片晶圓速度進行單次曝光的設備,在進行雙重曝光時速度會降至一半,而隨著額外圖案化步驟的增加,效率會進一步下降。

良率問題

良率(每片晶圓功能性晶片的百分比)是另一個主要挑戰。行業分析師預測,中芯國際的 5nm 製程的良率可能只有台積電同等技術的約三分之一。

林本堅指出,多重圖案化不僅耗時,如果曝光未能完美執行,還可能導致更低的良率。四重圖案化過程中自對準的困難直接影響良率和處理速度。

應用與使用案例

中芯國際先進製造工藝的主要客戶是華為。目前,中芯國際的 7nm N+2 製程用於華為的麒麟 9000s 和麒麟 9010 處理器,分別為 Mate 60 Pro 和 Pura 70 智能手機提供動力。

展望未來,華為據報導計劃使用中芯國際的 5nm 技術來製造其 Ascend 910C AI 晶片,旨在減少中國對 NVIDIA 的依賴。這種在 AI 加速方面的應用代表著中國半導體獨立的戰略優先事項。

地緣政治背景與未來展望

美國出口限制影響

中芯國際在沒有 EUV 的情況下追求先進製造的努力是在美國貿易限制的背景下進行的,這些限制限制了中國獲取尖端半導體技術的能力。這些限制阻止了中芯國際從荷蘭公司 ASML(專門製造這項技術的公司)獲得 EUV 光刻機。

這些限制迫使中國公司探索替代方法並發展國內能力。正如林本堅所指出的,「北京已採取『舉國體制』戰略來促進其晶片產業」。

國內技術發展

對於 5nm 節點以外的長期競爭力,專家認為中國最終將需要獲取或開發自己的 EUV 技術。為此,中國正在追求國內替代方案:

- 國有晶片製造設備開發商 SiCarrier(據報導與華為有關)正在開發 ASML 工具的替代品

- 華為正在評估一種自主開發的基於雷射誘導放電等離子體(LDP)的機器,但用於大規模生產的最終設備預計要到 2026 年才能完成

- 國產 EUV 相當技術的試生產可能最早於 2025 年第三季度開始

中芯國際 5nm 與台積電 5nm 製程比較

中芯國際的 5nm 製程與台積電的 5nm 技術存在顯著差異,主要體現在光刻技術、成本結構、良率表現與技術限制突破:

關鍵差異分析

| 比較項目 | 中芯國際 5nm (N+2) | 台積電 5nm (N5) |

|---|---|---|

| 光刻技術 | 使用 DUV + SAQP 多重曝光 | 採用 EUV 單次/雙次曝光 |

| 生產成本 | 比台積電高出 40-50% | 基於 EUV 的標準化成本 |

| 晶圓良率 | 約 30-40% | 超過 80% |

| 技術成熟度 | 依賴多重曝光與自對準四重成像 (SAQP) | 成熟 EUV 技術,良率穩定 |

| 應用產品 | 華為 Ascend 910C AI 晶片 | Apple A14、NVIDIA H100 等旗艦產品 |

1. 光刻技術與製程複雜度

中芯國際因無法取得 ASML 的 EUV 設備,改以深紫外光 (DUV) 搭配自對準四重成像 (SAQP) 技術,透過至少四次曝光與蝕刻步驟實現 5nm 精細度。相較之下,台積電的 EUV 技術僅需單次或雙次曝光即可達成相同節點,大幅簡化流程並減少誤差累積。

2. 成本與商業可行性

中芯國際的 5nm 晶圓生產成本比台積電高出 40-50%,主因多重曝光導致設備使用時間與耗材增加。以 2025 年數據估算,中芯國際每片 5nm 晶圓成本約 15,000 美元,而台積電僅需 10,000 美元。此外,中芯國際的良率僅台積電三分之一,進一步推升有效成本。

3. 性能與應用限制

儘管中芯國際的 5nm 製程能生產功能性晶片,但其電晶體密度與能耗表現仍落後台積電。TechInsights 分析指出,中芯國際的 7nm N+2 製程邏輯密度僅介於台積電 7nm 與 7nm+ 之間,推估 5nm 技術差距將更明顯。目前中芯國際 5nm 主要用於華為 AI 加速器,尚未達到手機處理器所需的效能與能耗標準。

中芯國際如何在沒有 EUV 設備的情況下實現 7nm 製程

中芯國際成功在未使用 EUV 設備下實現 7nm 製程,關鍵在於多重曝光技術與製程設計協同優化。以下是具體技術方法與產業影響分析:

核心技術原理

中芯國際採用深紫外光 (DUV) 設備結合自對準四重成像 (SAQP) 技術,透過以下步驟突破物理限制:

- 多重曝光流程:單一光刻層需進行 34 道步驟(相比 EUV 僅需 9 道),包含多次「光刻-蝕刻-沉積」循環

- SAQP 技術:透過四次圖案化步驟將線寬縮減至 20nm 以下,達成 7nm 節點所需精細度

- 浸潤式光刻:使用水作為介質提升 DUV 解析度至 38nm 極限

製程優化策略

| 優化層面 | 中芯國際 7nm (N+1) | 台積電 7nm (初代) |

|---|---|---|

| 邏輯密度 | 89 MTr/mm² | 91 MTr/mm² |

| 單元架構 | 6-track 單元設計 | 7-track 單元設計 |

| 接觸間距 | 60nm (類 10nm 規格) | 54nm |

| 效能平衡 | 犧牲部分性能換取製程可行性 | 全面優化性能與密度 |

TechInsights 分析顯示,中芯國際透過設計技術協同優化 (DTCO) 彌補設備限制:

- 導入單擴散斷點 (SDB) 技術減少單元面積

- 採用混合多重圖案化 (Hybrid Multi-Patterning) 降低掩模層數

- 優化金屬堆疊結構補償光刻解析度不足

產業影響與限制

技術突破意義:

- 驗證 DUV 設備在 7nm 節點的商業可行性

- 為中國半導體產業建立非 EUV 技術路線

- 華為麒麟 9000s 處理器實現 5G 整合晶片國產化

現實挑戰:

- 成本激增:每片晶圓成本比 EUV 製程高出 2.4 倍

- 良率限制:初期良率僅 30-40%,遠低於台積電的 80%

- 設計制約:需遵守嚴格設計規則 (DRC) 補償製程缺陷

- 設備耗損:多重曝光使 DUV 設備使用壽命縮短 40%

儘管如此,中芯國際的 7nm 製程已應用於比特礦機 ASIC 與手機處理器,2023 年產能提升至每月 15,000 片晶圓。此技術路徑證實,在 EUV 禁運下,中國仍能透過製程創新與系統級優化維持半導體技術進程。

FAQ

- 中芯國際如何在沒有 EUV 設備的情況下實現 5nm 製程?

中芯國際採用深紫外光 (DUV) 光刻結合自對準四重圖案化 (SAQP) 技術,透過多次曝光和蝕刻步驟來提升解析度,在設計和製程上進行協同優化以實現 5nm 節點功能。 - 中芯國際的 5nm 製程與台積電的 5nm 製程有何差異?

中芯國際無法使用 EUV 技術,改用 DUV 進行多重曝光,導致成本高出 40-50%,良率約為台積電的三分之一,但成功實現了基於中國半導體技術的自主創新。 - 使用 DUV 技術實現 5nm 節點有哪些挑戰?

使用 DUV 和多重圖案化 (SAQP) 技術會大幅增加生產成本、降低良率,且因多次曝光要求提高工藝精度,使生產效率相比 EUV 技術低許多。 - 中芯國際的 5nm 製程主要用在哪些領域?

中芯國際的 5nm 製程目前主要應用於支持華為的 Ascend 910C AI 加速器,用於人工智能運算,並減少對國外先進技術(如 NVIDIA)的依賴。 - 中國半導體未來的技術發展方向是什麼?

隨著美國的技術禁令,中國正積極研發自主 EUV 設備,例如基於雷射誘導放電等離子體 (LDP) 的技術,並有可能在 2025-2026 年投入試生產。

結論

中芯國際報導的向 5nm 晶片製造無 EUV 光刻的進展既代表技術成就,也是對地緣政治限制的回應。雖然使用 DUV 和四重圖案化的方法可以生產功能性 5nm 晶片,但與基於 EUV 的生產相比,在成本、效率和良率方面有顯著折衷。

這一進展展示了中國不顧出口限制發展半導體獨立性的決心。然而,巨大的成本溢價和良率挑戰表明,這種方法在全球市場中可能更具戰略能力價值,而非商業競爭力。中國半導體產業未來的競爭力可能最終取決於其開發國產 EUV 等效技術的能力。

需要特別注意的是,這一技術路徑證明,即使在嚴格的技術封鎖下,通過創新製程和設計優化,仍能實現先進晶片製造,這對全球半導體產業格局具有深遠影響。